计算机组成原理—存储器

计算机组成原理—硬件结构

二、存储器

1.概述

存储器是计算机系统中的记忆设备,用来存放程序和数据

1.1存储器的层次结构

缓存-主存层次主要解决CPU和主存速度不匹配的问题,速度接近缓存

主存-辅存层次主要解决存储系统的容量问题,容量接近与价位接近于主存

2.主存储器

2.1概述

主存与CPU的联系

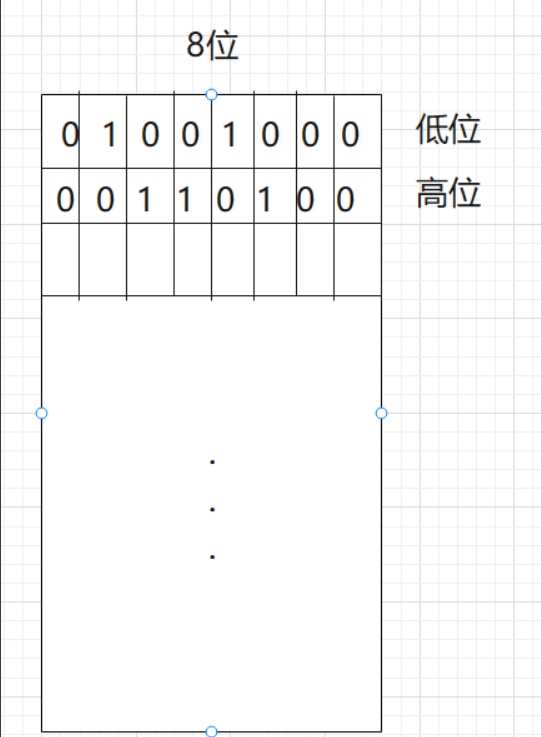

- 主存中存储单元地址的分配

主存各存储单元的空间是由单元地址号来表示。

字地址使用该地址高位字节的地址来表示,其字地址是4的整数倍,正好用地址码的末两位来区别

高地址存高位数据

低地址存低位数据

设地址线24位

若字长8位,按字节寻址的范围是16M(2的24次方)

若字长16位,按字节寻址的范围是8M

若字32位,按字节寻址的范围是4M

- 主存的计数指标

主要指标是存储容量和存储速度

存储容量:存储单元个数*存储字长(注意单位,是否除以8)

存储速度,分为存取时间和存取周期

存储器带宽:频率*位数(1ns = 1MHz)

3.半导体存储芯片

3.1基本结构

3.2译码驱动方式

- 线选法:在矩阵中每次选一行

- 重合法:在矩阵中利用X/Y地址译码器找到1位

4.随机存取器

4.1静态RAM(SRAM)

静态RAM是用触发器工作原理存储信息的,存储信息会保持原状态,不需要再生

4.1.1SRAM单元电路

4.SRAM的举例

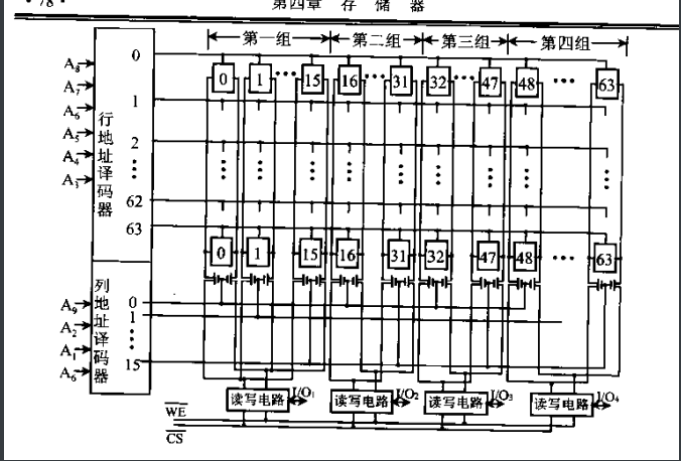

以Intel 2144为例,1k*4(10根地址线,4根数据线)

其内部存储矩阵如下图所示

此结构将列分为4个组,每组16列,存取时,正好在每组拿一列,4位输出/输入

4.2动态RAM(DRAM)

常见的动态RAM的基本单元电路有三管式和但管式两种,都是靠电容存储电荷原理来寄存信息。需要刷新,一般间隔2ms(一次存取)

4.2.1三管式

单元电路

其中的存储的0/1与原存信息是相反的

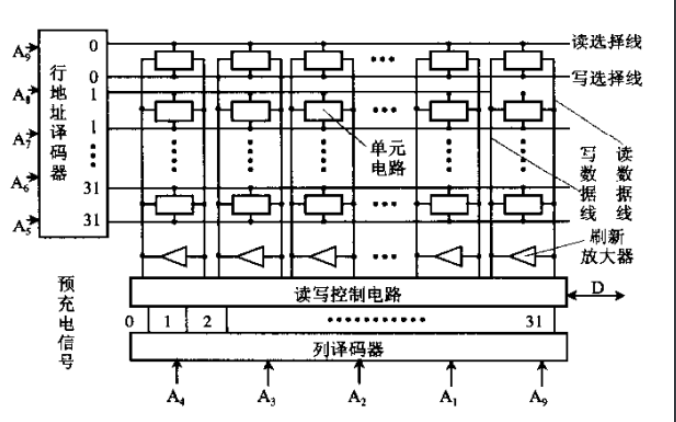

1k*1结构示意图

4.2.2单管式

单元电路

16k*1结构示意图

注:此时用了地址线的复用,先行地址,在列地址

4.3刷新

刷新是一行一行的刷新

4.3.1集中刷新

在2ms内选一个时间段进行刷新,会存在"死区"(不能进行任何操作)

4.3.2分散刷新

每行都进行一次集中刷新,无"死区",但会使存取周期变长

4.3.3异步刷新

将上述两种方法结合,在2ms内寻找完成每一行刷新需要的时间间隔,在这个间隔内做一次集中刷新

4.3.4指令译码阶段刷新

不会出现"死区"

4.4静态和动态的比较

| 动态RAM | 静态RAM | |

|---|---|---|

| 集成度 | 高 | 低 |

| 封装性 | 低 | 高 |

| 功耗 | 低 | 高 |

| 价格 | 低 | 高 |

| 速度 | 低 | 高 |

| 刷新 | 需要 | 不需要 |

5.存储器与CPU的连接

5.1存储容量的扩展

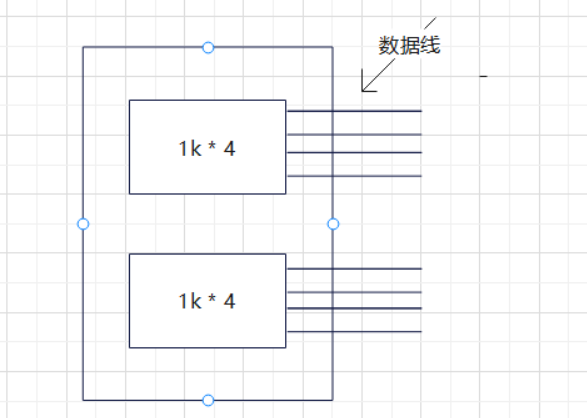

- 位扩展

位扩展是指增加字长,eg:1k * 4的芯片可以变成1k * 8的

- 字扩展

字扩展是指增加存储器字的数量,eg:1k * 8的芯片可以变成2k * 8的

- 字,位扩展

将上面两种扩展结合

5.2存储器和CPU的连接

- 选择合适的芯片(种类,个数)

- 数据线

- 地址线

- 控制线

- 片选信号:位扩展:串联(一起选用);字扩展:互斥(只用一个)

5.2.1数据线(2个为例)

- 位扩展:一个芯片连高位,一个芯片连接低位

- 字扩展:对应相连即可

5.2.2地址线

- 位扩展:对应相连即可

- 字扩展:先连低位,如有剩余,则连片选等

5.2.3控制

- 若只有一个读写,则连接MAR

5.2.4片选信号

基本思想:位扩展:串联(一起选用);字扩展:互斥(只用一个)

6.存储器地校验

6.1汉明码地组成

汉明码具有一位纠错能力,默认偶检验(可以改为奇检验)

汉明码 = 信息码 + 校验码

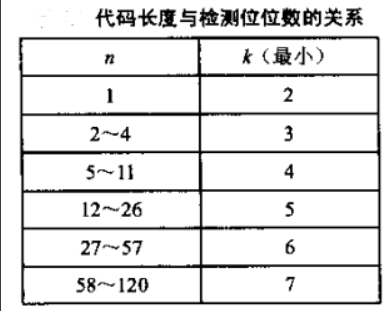

设信息码个数为n,校验码地个数为k,则要满足n + k <= 2^k - 1

- 校验码的存放位置

从低到高位依次为,2^k(k从零开始...)

- 校验码0/1的选择

若是偶检验,使该位与其校验位的1的个数为偶数;奇检验反之

- 判断与之对应的校验位

将所有位数的二进制写出,位数由校验码的个数而定,将1作为对应的标准

eg:4位信息码,3位校验码

C是校验码,b是信息码

C1的校验位:3、5、7、(9)

C2的校验位:3、6、7、(10)

C3的校验位:5、6、7

(C4的校验位:9、10)

6.2纠错过程

由上述的规则来判断是哪一位的0/1出错

注:有的位置被多个校验码校验,注意检查

7.提高访存速度的措施

7.1单体多字系统

如下图,可以使主存宽带提高4倍,提高了单体存储器的工作速度

7.2多体并行系统

- 高位交叉编址的多体存储器

- 低位交叉编址的多体存储器

若存期周期位T,总线传输速率为r

低位:t = T + (n-1) * r

高位:t = n * T

8.高速缓存存储器

8.1概述

Cache-主存存储空间的基本结构

CPU读取主存某字时,有命中和不命中两种

- 命中:主存块已调入缓存块

- 不命中:欲访问的主存块没有调入缓存块

有关命中率的计算

命中率 = 命中次数/总访问次数

平均访问时间 = 命中率 * 访问Cache的时间 + 未命中率 * 访问主存的时间

访问效率 = 访问Cache的时间 / 平均访问时间 * 100%

8.2Cache-主存地址映射

计算主存地址时,从右往左算(2的多少次方)

- 直接映射

每个主存块只与一个缓存块对应

字块内地址:判断字字块的存错单元的个数

Cache字块地址:判断Cache的块数

主存块标记:判断主存的块数,并减去上述两个位数的和

- 全相联映射

每个主存块与任意缓存块对应

字块内地址:判断字字块的存错单元的个数

主存块标记:判断主存的块数,并减去上述位数

- 组相联映射

主存块只与一个缓存组对应,每个主存块与对应缓存组的任意缓存块对应

字块内地址:判断字字块的存错单元的个数

组地址:判断Cache的组数

主存块标记:判断主存的块数,并减去上述两个位数的和